Technical documentation

Support & training

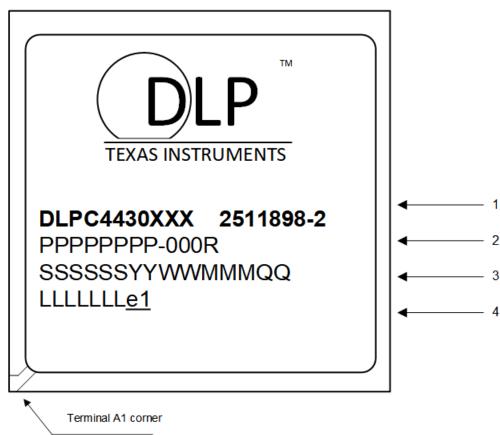

**DLPC4430** DLPS223 - DECEMBER 2021

# **DLPC4430 DLP® Display Controller**

## 1 Features

- Single DLP controller support for up to WUXGA resolution display using digital micromirror devices (DMDs):

- Up to 1920x1200 at 120Hz (2D and 3D)

- Provides single 30-bit or dual 60-bit input pixel interface:

- RGB data format

- 8.9 or 10 bits per Color

- Pixel clock up to 320 MHz in dual 30-bit mode on single controller

- High-speed, low voltage differential signaling (LVDS) DMD interface

- 150 MHz ARM946<sup>™</sup> microprocessor

- Microprocessor peripherals

- Programmable pulse-width modulation (PWM) and capture timers

- Three I<sup>2</sup>C ports, Three UART ports and three \_ SSP ports

- One USB 1.1 secondary port

- Image processing

- Multiple image processing algorithms

- Frame rate conversion

- Color coordinate adjustment

- Programmable color space conversion

- Programmable degamma and splash

- Integrated support for 3-D display

- 2-D keystone correction

- Integrated clock generation circuitry

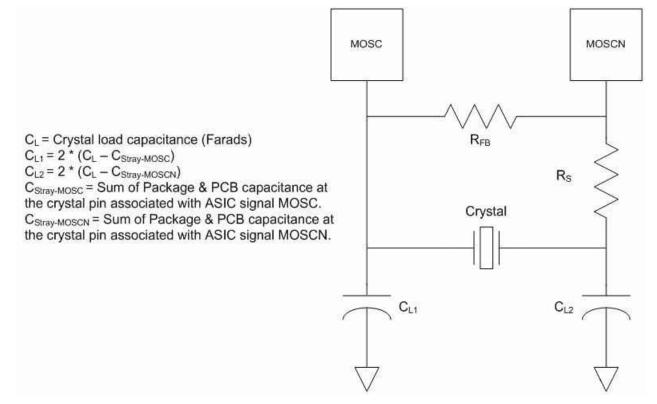

- Operates on a single 20 MHz crystal

- Integrated spread spectrum clocking

- External memory support

- Parallel flash for microprocessor and PWM sequence

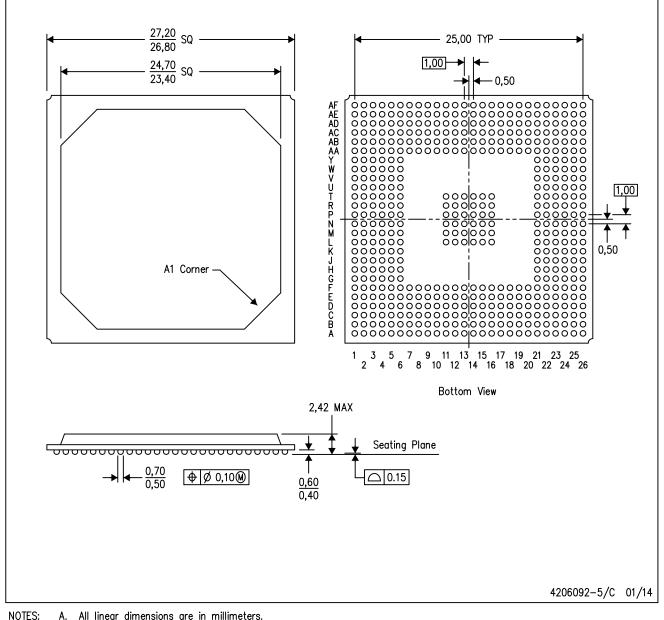

- 516 pin plastic ball grid array package

- Supports LED, and laser hybrid illuminations

#### 2 Applications

- Laser TV

- Smart projector

- **Digital signage**

- Enterprise projectors

## **3 Description**

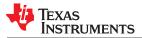

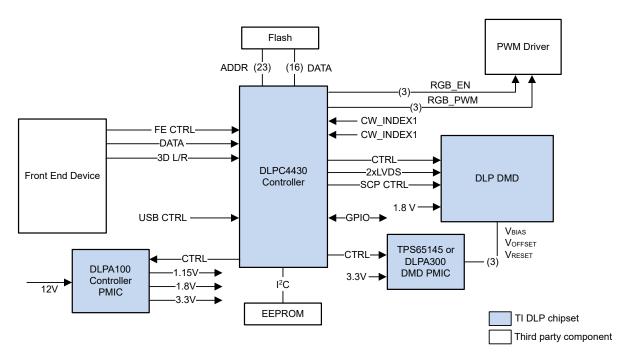

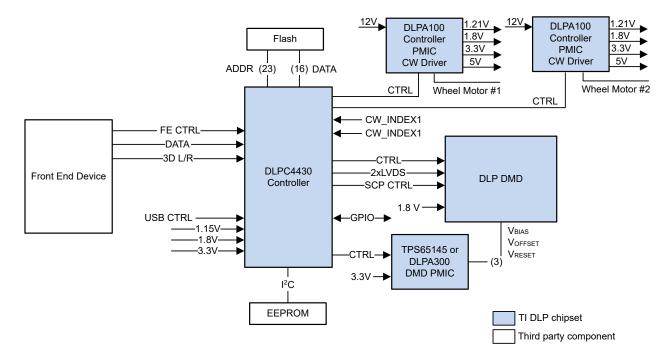

The DLPC4430 is a digital display controller for the DLP display chipset. The chipset is comprised of DLPC4430 display controller, DLP DMD, DLPA100 controller power management device and DLPA300 -DMD power management device (refer to the DMD data sheet). This solution is a great fit for display systems that require high resolution, high brightness and system simplicity. To ensure reliable operation, the DLPC4430 display controller must always be used with a DLP DMD and respective power management devices.

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE   | BODY SIZE (NOM)     |  |  |  |  |

|----------------------------|-----------|---------------------|--|--|--|--|

| DLPC4430                   | ZPC (516) | 27.00 mm × 27.00 mm |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Simplified Schematic**

## **Table of Contents**

| 1 Features1                                         |

|-----------------------------------------------------|

| 2 Applications1                                     |

| 3 Description1                                      |

| 4 Revision History2                                 |

| 5 Pin Configuration and Functions                   |

| 6 Specifications14                                  |

| 6.1 Absolute Maximum Ratings14                      |

| 6.2 ESD Ratings14                                   |

| 6.3 Recommended Operating Conditions15              |

| 6.4 Thermal Information15                           |

| 6.5 Electrical Characteristics15                    |

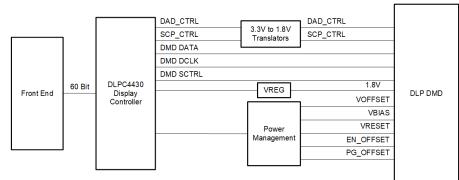

| 6.6 System Oscillators Timing Requirements          |

| 6.7 Test and Reset Timing Requirements              |

| 6.8 JTAG Interface: I/O Boundary Scan Application   |

| Timing Requirements 19                              |

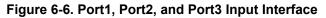

| 6.9 Port 1 Input Pixel Timing Requirements          |

| 6.10 Port 3 Input Pixel Interface (via GPIO) Timing |

| Requirements20                                      |

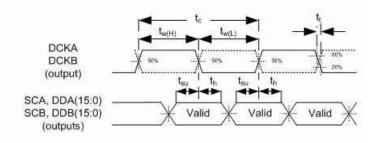

| 6.11 DMD LVDS Interface Timing Requirements21       |

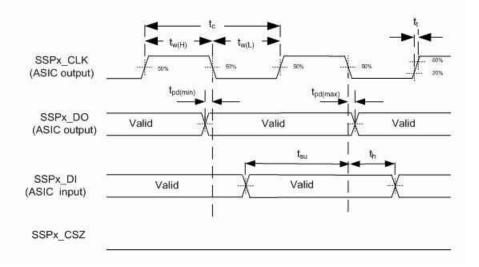

| 6.12 Synchronous Serial Port (SSP) Interface        |

| Timing Requirements21                               |

| 6.13 Programmable Output Clocks Switching           |

| Characteristics22                                   |

| 6.14 Synchronous Serial Port Interface (SSP)        |

| Switching Characteristics22                         |

| 6.15 JTAG Interface: I/O Boundary Scan Application  |

| Switching Characteristics23                         |

|                                                     |

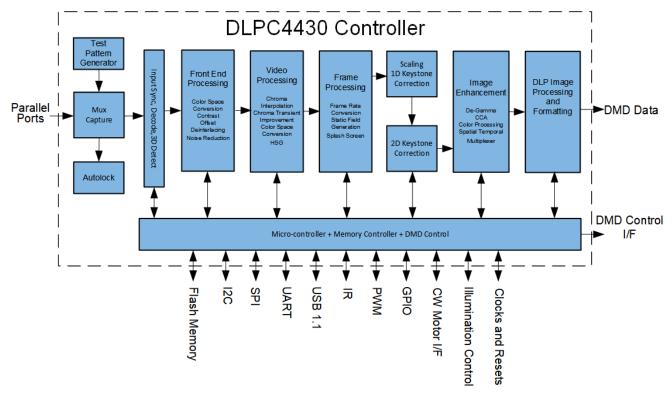

| 7 Detailed Description                               | 26 |

|------------------------------------------------------|----|

| 7.1 Overview                                         |    |

| 7.2 Functional Block Diagram                         | 26 |

| 7.3 Feature Description                              |    |

| 7.4 Device Functional Modes                          |    |

| 8 Application and Implementation                     | 31 |

| 8.1 Application Information                          |    |

| 8.2 Typical Application                              |    |

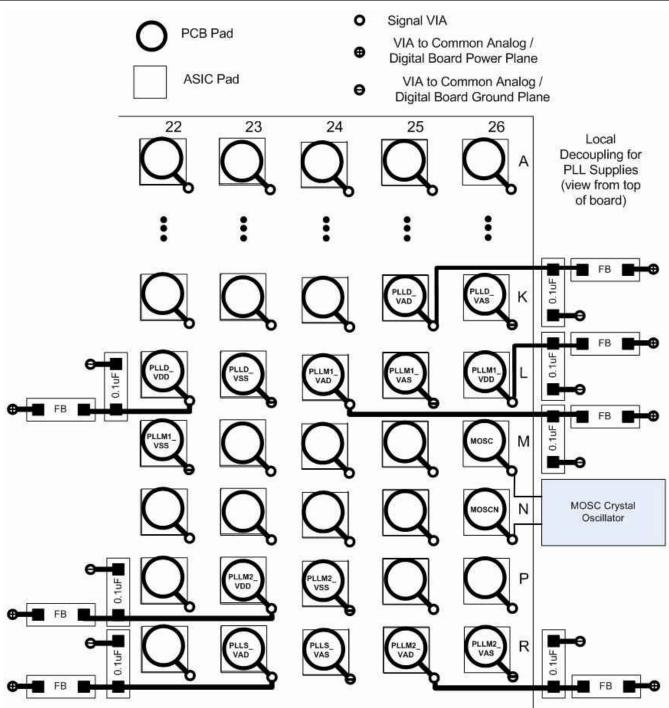

| 9 Power Supply Recommendations                       |    |

| 9.1 System Power Regulations                         |    |

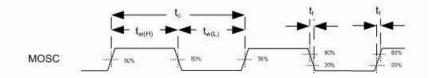

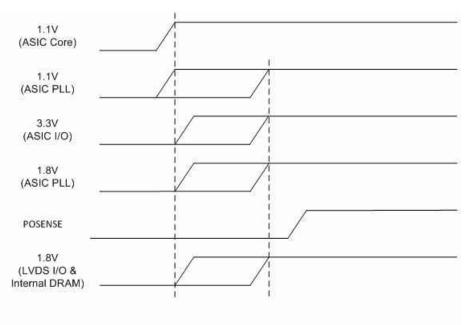

| 9.2 System Power-Up Sequence                         |    |

| 9.3 Power-On Sense (POSENSE) Support                 |    |

| 9.4 System Environment and Defaults                  |    |

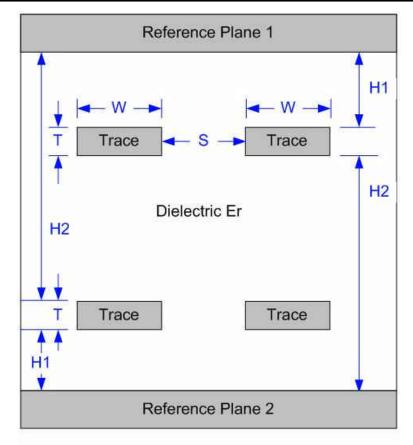

| 10 Layout                                            |    |

| 10.1 Layout Guidelines                               |    |

| 11 Device and Documentation Support                  | 43 |

| 11.1 Device Support                                  |    |

| 11.2 Documentation Support                           |    |

| 11.3 Receiving Notification of Documentation Updates | 45 |

| 11.4 Support Resources                               | 45 |

| 11.5 Trademarks                                      | 45 |

| 11.6 Electrostatic Discharge Caution                 | 45 |

| 11.7 Glossary                                        | 45 |

| 12 Mechanical, Packaging, and Orderable              |    |

| Information                                          | 46 |

## **4 Revision History**

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2021 | *        | Initial release. |

## **5** Pin Configuration and Functions

|   | 20 | 25 | 24 | 8  | 23 | 24 | 20 | 19 | 18 | 11 | 16             | ŝ  | 14 | 13 | 2 | Ξ | 1  | æ  | 8  | 7 | 9 | 'n | 4 | e | 2 | Ť. |  |

|---|----|----|----|----|----|----|----|----|----|----|----------------|----|----|----|---|---|----|----|----|---|---|----|---|---|---|----|--|

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | o  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | o | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | Î. |    |    |    |                |    |    |    |   |   |    |    |    | - | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | o | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0              | 0  | 0  | 0  | 0 | 0 |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0              | 0  | 0  | 0  | 0 | 0 |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0              | 0  | 0  | 0  | 0 | 0 |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0              | 0  | 0  | 0  | 0 | 0 |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0              | 0  | 0  | 0  | 0 | 0 |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | ¢  | 0  | 0  |    |    |    |    | 0              | 0  | 0  | 0  | 0 | 0 |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |                |    |    |    |   |   |    |    |    |   | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0              | 0  | 0  | 0  | 0 | 0 | 0  | 0  | 0  | 0 | 0 | 0  | 0 | 0 | 0 | 0  |  |

| - | 38 | 26 | 24 | 23 | 22 | 21 | 20 | 5  | 48 | 17 | <del>1</del> 8 | \$ | 쁖  | 5  | 4 | Ę | 10 | đì | 03 | ~ | œ | ця | 4 | e | 2 | ÷  |  |

Figure 5-1. ZPC Package 516-Pin BGA Bottom View

#### Table 5-1. Pin Functions

| PIN <sup>(1)</sup> I/O <sup>(2)</sup> NAME         NO. |                    | HO(2)                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|--------------------------------------------------------|--------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                        |                    | · //O(2)               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

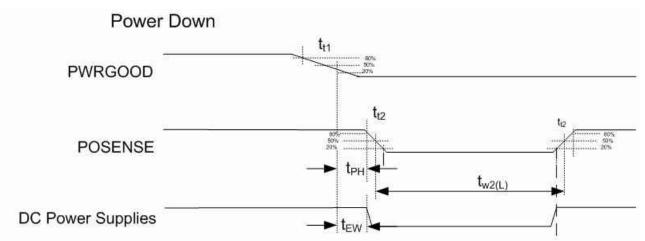

| POSENSE                                                | P22                | I <sub>4</sub>         | Power-On Sense, High true, signal provided from an external voltage monitor circuit. This signal is driven active (high) when all ASIC supply voltages have reached 90% of their specified minimum voltage. This signal is driven inactive (low) after the falling edge of PWRGOOD as specified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PWRGOOD                                                | T26                | 14                     | Power Good, High true, signal from external power supply or voltage monitor. A high value indicates all power is within operating voltage specs and the system is safe to exit its reset state. A transition from high to low is used to indicate that the controller or DMD supply voltage drops below their rated minimum level. This transition must occur prior to the supply voltage drop as specified. During this interval, POSENSE must remain active high. This is a warning of an imminent power loss condition. This warning is required to enhance long term DMD reliability. A DMD park followed by a full controller reset is performed by the DLPC4430 controller when PWRGOOD goes low for the specified minimum, protecting the DMD. This minimum de-assertion time is used to protect the input from glitches. Following this the DLPC4430 controller is held in its reset state as long as PWRGOOD is low. PWRGOOD must be driven high for normal operation. The DLPC4430 controller acknowledges PWRGOOD as active once it has been driven high for a specified minimum time. Uses hysteresis. |  |  |  |

| EXT_ARTZ                                               | T24                | O <sub>2</sub>         | General purpose, LOW true, reset output. This output is asserted low immediately upon asserting power-up reset (POSENSE) low and remains low while POSENSE remains low. EXT_ARSTZ continues to be held low after the release of power-up reset (that is, POSENSE set high) until released by software. EXT_ARSTZ is also asserted low approximately 5µs after the detection of a PWRGOOD or any internally generated reset. In all cases it remains active for a minimum of 2ms. Note that the ASIC contains a software register that can be used to independently drive this output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| MTR_ARTZ                                               | T25                | O <sub>2</sub>         | Color wheel motor controller, LOW true, reset output. This output is asserted low immediately upon asserting<br>power-up reset (POSENSE) low and remains low while POSENSE remains low. MTR_ARSTZ continues to be held<br>low after the release of power-up reset (i.e. POSENSE set high) until released by software. MTR_ARSTZ is also<br>optionally asserted low approximately 5 µs after the detection of a PWRGOOD or any internally generated reset. In<br>all cases it remains active for a minimum of 2 ms. Note that the ASIC contains a software register that can be used to<br>independently drive this output. The ASIC also contains a software register that can be used to disable the assertion<br>of motor reset upon a lamp strike reset.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| BOARD LEVEL TEST                                       | AND INITIALIZATION | (3)                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| TDI                                                    | N25                | I <sub>4</sub>         | JTAG serial data in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| тск                                                    | N24                | I <sub>4</sub>         | JTAG serial data clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| TMS1                                                   | P25                | I <sub>4</sub>         | JTAG test mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| TMS2                                                   | P26                | I <sub>4</sub>         | JTAG test mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| TDO1                                                   | N23                | O <sub>5</sub>         | JTAG serial data out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| TDO2                                                   | N22                | 0 <sub>5</sub>         | JTAG serial data out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| TRSTZ                                                  | M23                | I <sub>4</sub>         | JTAG reset. This signal includes an internal pull-up and utilizes hysteresis. This pin is pulled high (or left unconnected) when the JTAG interface is in use for boundary scan or ARM debug. Connect this pin to ground otherwise. Failure to tie this pin low during normal operation will cause startup and initialization problems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RTCK                                                   | E4                 | 0 <sub>2</sub>         | JTAG Return Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ETM_PIPESTAT_2                                         | A4                 | B <sub>2</sub>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ETM_PIPESTAT_1                                         | B5                 | B <sub>2</sub>         | ETM Trace Port Pipeline Status. Indicates the pipeline status of the ARM core. These signals include internal<br>pull-downs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ETM_PIPESTAT_0                                         | C6                 | B <sub>2</sub>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ETM_TRACESYNC                                          | A5                 | B <sub>2</sub>         | ETM Trace Port Synchronization signal, indicating the start of a branch sequence on the trace packet port. This signal includes an internal pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| ETM_TRACECLK                                           | D7                 | B <sub>2</sub>         | ETM Trace Port Clock. This signal includes an internal pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ICTSEN                                                 | M24                | I <sub>4</sub>         | IC Tri-State Enable (active high). Asserting high will Tri-state all outputs except the JTAG interface. This signal<br>includes an internal pull-down, however an external pull-down is recommended for added protection. Uses<br>hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| TSTPT_7                                                | E8                 | B <sub>2</sub>         | Test pin 7 - This signal provides internal pull-downs.<br>Normal Use: reserved for test output. Recommended to be left open or unconnected for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TSTPT_6                                                | B4                 | B <sub>2</sub>         | Test pin 6 - This signal provides internal pull-downs.           Normal Use: reserved for test output. Recommended to be left open or unconnected for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| TSTPT_5                                                | C4                 | B <sub>2</sub>         | Test pin 5 - This signal provides internal pull-downs.<br>Normal Use: reserved for test output. Recommended to be left open or unconnected for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TSTPT_4                                                | E7                 | B <sub>2</sub>         | Test pin 4 - This signal provides internal pull-downs.<br>Normal Use: reserved for test output. Recommended to be left open or unconnected for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TSTPT_3                                                | D5                 | B <sub>2</sub>         | Test pin 3 - This signal provides internal pull-downs.<br>Normal Use: reserved for test output. Recommended to be left open or unconnected for normal use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TSTPT_2                                                | E6                 | B <sub>2</sub>         | Test pin 2 - This signal provides internal pull-downs. Additionally, it is recommended that jumper options be provided for connecting TSTPT(2:0) to external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| TSTPT_1                                                | D3                 | B <sub>2</sub>         | Test pin 1 - This signal provides internal pull-downs. Additionally, it is recommended that jumper options be provided for connecting TSTPT(2:0) to external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| TSTPT_0                                                | C2                 | B <sub>2</sub>         | Test pin 0 - This signal provides internal pull-downs. Additionally, it is recommended that jumper options be provided for connecting TSTPT(2:0) to external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| DEVICE TEST                                            |                    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| HW_TEST_EN                                             | M25                | I <sub>4</sub>         | Device manufacturing test enable: This signal includes an internal pull-down and utilizes hysteresis. It is recommended that this signal be tied to an external ground in normal operation for added protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PORT1 and PORT 2 C                                     | HANNEL DATA and    | CONTROL (4) (5) (6) (7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| PIN(1)           NAME         NO. |      |                      |                                                                                                                                                                                             |  |  |  |

|-----------------------------------|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                   |      | - I/O <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                                 |  |  |  |

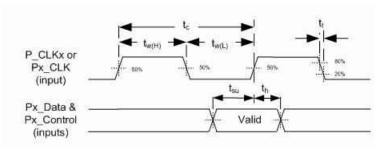

| P_CLK1                            | AE22 | I <sub>4</sub>       | Input Port Data Pixel Write Clock (selectable as rising or falling edge triggered, and which port it is associated wit<br>or B or (A and B))). This signal includes an internal pull-down.  |  |  |  |

| P_CLK2                            | W25  | I <sub>4</sub>       | Input Port Data Pixel Write Clock (selectable as rising or falling edge triggered, and which port it is associated with (A or B or (A and B))). This signal includes an internal pull-down. |  |  |  |

| P_CLK3                            | AF23 | I <sub>4</sub>       | Input Port Data Pixel Write Clock (selectable as rising or falling edge triggered, and which port it is associated with (A or B or (A and B))). This signal includes an internal pull-down. |  |  |  |

| P_DATAEN1                         | AF22 | I <sub>4</sub>       | Active High Data Enable. Selectable as to which port it is associated with (A or B or (A and B)). This signal includes an internal pull-down.                                               |  |  |  |

| P_DATAEN2                         | W24  | I <sub>4</sub>       | Active High Data Enable. Selectable as to which port it is associated with (A or B or (A and B)). This signal includes an internal pull-down.                                               |  |  |  |

| P1_A_9                            | AD15 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 128)                                                                                                                                          |  |  |  |

| P1_A_8                            | AE15 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 64)                                                                                                                                           |  |  |  |

| P1_A_7                            | AE14 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 32)                                                                                                                                           |  |  |  |

| P1_A_6                            | AE13 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 16)                                                                                                                                           |  |  |  |

| P1_A_5                            | AD13 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 8)                                                                                                                                            |  |  |  |

| P1_A_4                            | AC13 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 4)                                                                                                                                            |  |  |  |

| P1 A 3                            | AF14 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 2)                                                                                                                                            |  |  |  |

|                                   | AF13 |                      | Port 1 A Channel Input Pixel Data (bit weight 1)                                                                                                                                            |  |  |  |

| P1_A_2                            |      | I <sub>4</sub>       |                                                                                                                                                                                             |  |  |  |

| P1_A_1                            | AF12 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 0.5)                                                                                                                                          |  |  |  |

| P1_A_0                            | AE12 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 0.25)                                                                                                                                         |  |  |  |

| P1_B_9                            | AF18 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 128)                                                                                                                                          |  |  |  |

| P1_B_8                            | AB18 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 64)                                                                                                                                           |  |  |  |

| P1_B_7                            | AC15 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 32)                                                                                                                                           |  |  |  |

| P1_B_6                            | AC16 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 16)                                                                                                                                           |  |  |  |

| P1_B_5                            | AD16 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 8)                                                                                                                                            |  |  |  |

| P1_B_4                            | AE16 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 4)                                                                                                                                            |  |  |  |

| P1_B_3                            | AF16 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 2)                                                                                                                                            |  |  |  |

| P1_B_2                            | AF15 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 1)                                                                                                                                            |  |  |  |

| P1_B_1                            | AC14 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 0.5)                                                                                                                                          |  |  |  |

| P1_B_0                            | AD14 | I <sub>4</sub>       | Port 1 B Channel Input Pixel Data (bit weight 0.25)                                                                                                                                         |  |  |  |

| P1_C_9                            | AD20 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 128)                                                                                                                                          |  |  |  |

| P1_C_8                            | AE20 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 64)                                                                                                                                           |  |  |  |

| P1_C_7                            | AE21 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 32)                                                                                                                                           |  |  |  |

| P1_C_6                            | AF21 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 16)                                                                                                                                           |  |  |  |

|                                   | AD19 |                      |                                                                                                                                                                                             |  |  |  |

| P1_C_5                            |      | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 8)                                                                                                                                            |  |  |  |

| P1_C_4                            | AE19 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 4)                                                                                                                                            |  |  |  |

| P1_C_3                            | AF19 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 2)                                                                                                                                            |  |  |  |

| P1_C_2                            | AF20 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 1)                                                                                                                                            |  |  |  |

| P1_C_1                            | AC19 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 0.5)                                                                                                                                          |  |  |  |

| P1_C_0                            | AE19 | I <sub>4</sub>       | Port 1 C Channel Input Pixel Data (bit weight 0.25)                                                                                                                                         |  |  |  |

| P1_VSYNC                          | AC20 | B <sub>2</sub>       | Port 1 Vertical Sync. This signal includes an internal pull-down. While intended to be associated with Port 1, it can be programmed for use with Port 2.                                    |  |  |  |

| P1_HSYNC                          | AD21 | B <sub>2</sub>       | Port 1 Horizontal Sync. This signal includes an internal pull-down. While intended to be associated with Port 1, it can be programmed for use with Port 2.                                  |  |  |  |

| P2_A_9                            | AD26 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 128)                                                                                                                                          |  |  |  |

| P2_A_8                            | AD25 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 64)                                                                                                                                           |  |  |  |

| P2_A_7                            | AB21 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 32)                                                                                                                                           |  |  |  |

| P2_A_6                            | AC22 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 16)                                                                                                                                           |  |  |  |

| P2_A_5                            | AD23 | I <sub>4</sub>       | Port 1 A Channel Input Pixel Data (bit weight 8)                                                                                                                                            |  |  |  |

| P2_A_4                            | AB20 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 4)                                                                                                                                            |  |  |  |

| <br>P2_A_3                        | AC21 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 2)                                                                                                                                            |  |  |  |

| P2_A_2                            | AD22 | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 1)                                                                                                                                            |  |  |  |

| P2_A_1                            | AE23 | I <sub>4</sub>       |                                                                                                                                                                                             |  |  |  |

| P2_A_1<br>P2_A_0                  | AB19 |                      | Port 2 A Channel Input Pixel Data (bit weight 0.5)                                                                                                                                          |  |  |  |

|                                   |      | I <sub>4</sub>       | Port 2 A Channel Input Pixel Data (bit weight 0.25)                                                                                                                                         |  |  |  |

| P2_B_9                            | Y22  | I <sub>4</sub>       | Port 2 B Channel Input Pixel Data (bit weight 128)                                                                                                                                          |  |  |  |

| P2_B_8                            | AB26 | I <sub>4</sub>       | Port 2 B Channel Input Pixel Data (bit weight 64)                                                                                                                                           |  |  |  |

| P2_B_7                            | AA23 | I <sub>4</sub>       | Port 2 B Channel Input Pixel Data (bit weight 32)                                                                                                                                           |  |  |  |

| PIN <sup>(1)</sup>   |              |                    | Table 5-1. Pin Functions (continued)                                                                                                                      |  |  |  |  |

|----------------------|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                 | NO.          | I/O <sup>(2)</sup> | DESCRIPTION                                                                                                                                               |  |  |  |  |

| P2_B_6               | AB25         | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 16)                                                                                                         |  |  |  |  |

| P2_B_5               | AA22         | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 8)                                                                                                          |  |  |  |  |

| P2 B 4               | AB24         | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 4)                                                                                                          |  |  |  |  |

| P2_B_3               | AC26         | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 2)                                                                                                          |  |  |  |  |

| P2_B_2               | AB23         |                    | Port 2 B Channel Input Pixel Data (bit weight 1)                                                                                                          |  |  |  |  |

| P2_B_1               | AC25         |                    | Port 2 B Channel Input Pixel Data (bit weight 0.5)                                                                                                        |  |  |  |  |

| P2 B 0               | AC24         | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 0.25)                                                                                                       |  |  |  |  |

| P2_C_9               | W23          | I <sub>4</sub>     | Port 2 C Channel Input Pixel Data (bit weight 128)                                                                                                        |  |  |  |  |

| P2 C 8               | V22          | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 64)                                                                                                         |  |  |  |  |

| P2 C 7               | Y26          | I <sub>4</sub>     | Port 2 C Channel Input Pixel Data (bit weight 32)                                                                                                         |  |  |  |  |

| P2_C_6               | Y25          | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 16)                                                                                                         |  |  |  |  |

| P2_C_5               | Y24          | I <sub>4</sub>     | Port 2 C Channel Input Pixel Data (bit weight 8)                                                                                                          |  |  |  |  |

| P2_C_4               | Y23          | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 4)                                                                                                          |  |  |  |  |

| P2_C_3               | W22          |                    | Port 2 C Channel Input Pixel Data (bit weight 2)                                                                                                          |  |  |  |  |

|                      | AA26         | I <sub>4</sub>     |                                                                                                                                                           |  |  |  |  |

| P2_C_2               | AA20<br>AA25 |                    | Port 2 B Channel Input Pixel Data (bit weight 1)                                                                                                          |  |  |  |  |

| P2_C_1               |              | l <sub>4</sub>     | Port 2 C Channel Input Pixel Data (bit weight 0.5)                                                                                                        |  |  |  |  |

| P2_C_0               | AA24         | I <sub>4</sub>     | Port 2 B Channel Input Pixel Data (bit weight 0.25)                                                                                                       |  |  |  |  |

| P2_VSYNC             | U22          | B <sub>2</sub>     | Port 2 Vertical Sync. This signal includes an internal pull-down. While intended to be associated with Port 2, it can be programmed for use with Port1.   |  |  |  |  |

| P2_HSYNC             | W26          | B <sub>2</sub>     | Port 2 Horizontal Sync. This signal includes an internal pull-down. While intended to be associated with Port 2, it can be programmed for use with Port1. |  |  |  |  |

| ALF INPUT PORT CO    | ONTROL       |                    |                                                                                                                                                           |  |  |  |  |

| ALF_VSYNC            | AF11         | I <sub>4</sub>     | Autolock dedicated vertical sync. This signal includes an internal pull-down and uses hysteresis.                                                         |  |  |  |  |

| ALF_HSYNC            | AD11         | I <sub>4</sub>     | Autolock dedicated horizontal sync. This signal includes an internal pull-down and uses hysteresis.                                                       |  |  |  |  |

| ALF_CSYNC            | AE11         | I <sub>4</sub>     | Autolock dedicated composite sync (sync on green). This signal includes an internal pull-down and uses hysteresis.                                        |  |  |  |  |

| DMD RESET and BIA    | AS CONTROL   |                    |                                                                                                                                                           |  |  |  |  |

| DADOEZ               | AE7          | O <sub>5</sub>     | DAD (DLPA200 / DLPA300)Output Enable (active low)                                                                                                         |  |  |  |  |

| DADADDR_3            | AD6          | O <sub>5</sub>     |                                                                                                                                                           |  |  |  |  |

| DADADDR_2            | AE5          | O <sub>5</sub>     |                                                                                                                                                           |  |  |  |  |

| DADADDR_1            | AF4          | O <sub>5</sub>     | DAD address                                                                                                                                               |  |  |  |  |

| DADADDR_0            | AB8          | O <sub>5</sub>     | —                                                                                                                                                         |  |  |  |  |

| DADMODE_1            | AD7          | O <sub>5</sub>     |                                                                                                                                                           |  |  |  |  |

| DADMODE_0            | AE6          | O <sub>5</sub>     | DAD modes                                                                                                                                                 |  |  |  |  |

| DADSEL_1             | AE4          | O <sub>5</sub>     |                                                                                                                                                           |  |  |  |  |

| DADSEL 0             | AC7          | O <sub>5</sub>     | DAD select                                                                                                                                                |  |  |  |  |

| DADSTRB              | AF5          | O <sub>5</sub>     | DAD strobe                                                                                                                                                |  |  |  |  |

| DAD INTZ             | AC8          | I <sub>4</sub>     | DAD interrupt (active low). This signal typically requires an external pull-up and uses hysteresis.                                                       |  |  |  |  |

| DMD LVDS INTERFA     | CE           |                    |                                                                                                                                                           |  |  |  |  |

| DCKA P               | V4           | O <sub>7</sub>     |                                                                                                                                                           |  |  |  |  |

| DCKA N               | V3           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential clock                                                                                                               |  |  |  |  |

| SCA P                | V2           | 0 <sub>7</sub>     |                                                                                                                                                           |  |  |  |  |

| SCA_N                | V1           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial control                                                                                                      |  |  |  |  |

| DDA P 15             | P4           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_N_15             | P3           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_P_14             | P2           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_P_14<br>DDA_N_14 | P1           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_N_12             | R1           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_N_12<br>DDA_P_11 | T4           | 0 <sub>7</sub>     |                                                                                                                                                           |  |  |  |  |

| DDA_P_11<br>DDA_N_11 | T3           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_P_10             | T2           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

|                      | T1           | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_N_10             | U4           |                    | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_P_9              | U4<br>U3     | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_N_9              |              | 0 <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_P_8              | U2           | 07                 | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| DDA_N_8              | U1           | O <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data                                                                                                         |  |  |  |  |

| PIN <sup>(1)</sup> |                       |                    |                                                      |  |  |  |

|--------------------|-----------------------|--------------------|------------------------------------------------------|--|--|--|

| NAME               | NO.                   | I/O <sup>(2)</sup> | DESCRIPTION                                          |  |  |  |

| DDA_P_7            | W4                    | O <sub>7</sub>     | MD, LVDS I/F channel A, differential serial data     |  |  |  |

| DDA_N_7            | W3                    | O <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data    |  |  |  |

| DDA_P_6            | W2                    | O <sub>7</sub>     | DMD, LVDS I/F channel A, differential serial data    |  |  |  |